VMESCmodule2 / VMESCmodule2e

VME System Controller Core 2(e)

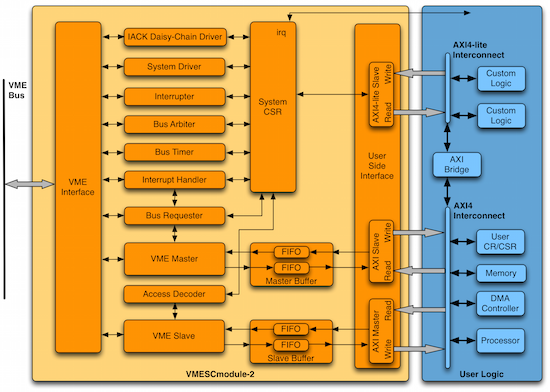

The VMESCmodule2 is Inicore's next generation VME System Controller core designed for FPGA and ASIC integrations. The core contains VME Slave and Master functions as well as System Controller features such as bus timer, arbiter, IACK daisy-chain driver, system clock driver and provisioning for CSR.

The AXI4 compliant user-side interface simplifies system integration. The core contains internal FIFOs and address mapping logic to bridge the VME to the AXI bus and vice versa. A dedicated AXI4-lite port is provided for independent CSR access.

With this rich feature set, the core can be used as a System Controller Module, as a Master Module, or as a Slave Module. This makes the VMESCmodule2 an excellent platform to base all your future VME designs on.

This core is available in two different flavors: VMESCmodule2e contains support for 2eSST while the VMESCmodule2 does not support 2eSST. Otherwise, their features are identical.

Block Diagram

Features

System Controller

- Bus Arbiter

- Bus Timer

- SYSCLOCK* driver

- SYSFAIL* driver

- First Slot Detector

- IACK daisy-chain driver

Master Interface

- Coupled transfers for single data cycles, buffered transfers for multiple data cycles (block/burst transfers)

- Addressing modes: A16, A24, A32

- Data types: D08(EO), D16, D32

- Protocol: SCT, D32-BLT, D64-MBLT, D64-2eSST[1]

- Access modes: Read, write

- 8 master windows to map the AXI memory space into the VME memory space

- Separate 4k deep read and write FIFOs to decouple AXI and VME bus transactions

Slave Interface

- Addressing modes: A16, A24, A32

- Data types: D08(EO), D16, D32

- Protocols: SCT, D32-BLT, D64-MBLT, D64-2eSST[1]

- Access modes: Read, write, read-modify-write

- Selectable rescinding DTACK

- Provides big-endian to little-endian conversion option

- 8 slave windows that map the VME memory space into the AXI memory space

- Separate 4k deep read and write FIFOs to decouple VME and AXI transactions

- Optional AXI block data read-ahead to increase data throughput

- Interrupt Handler

- Automatically fetches STATUS/ID vector from pending VME interrupt requests

- Supports D08(O), D16, and D32

Interrupter

- D08(O) interrupt status vector

- Software interrupt request (ROAK)

- User interrupt request (RORA)

- Programmable interrupt level

Bus Requester

- Supports RWD (release when done) and ROR (release on request) arbitration schemes

- FAIR requester

- Supports early withdrawal of bus request

System CR/CSR

- Contains address decoding for CR/CSR space

- Accessible via VME and local bus

- Local status and configuration regs for

- Interrupter

- Interrupt handler

- Slave memory windows

- AXI memory windows

- Special functions

- 4 32-bit mailbox registers

- 4 8-bit semaphores

- Local interrupt controller

- VME interrupt controller

- Control and status register mapping according to VME64x standard

Local Bus Interface

- Standard AXI4 compliant bus interface

- Separate AXI4-lite port for CR/CSR access

- Optional big-endian to little-endian conversion

[1]: D64-2eSST is only supported by the VMESCmodule2e.

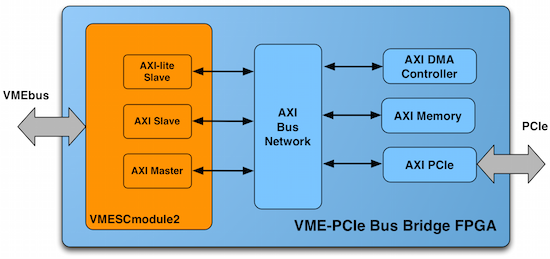

Application Example

Following figure shows the block diagram of a VME-to-PCIe bus bridge FPGA using a local AXI4 interconnect. The VMESCmodule2 is complemented by standard AXI based cores such as the AXI Bus Network, AXI DMA Controller, AXI Memory and the AXI PCIe interface to create the bus bridge functionality.

Highlights

- VME Master

- VME Slave

- VME System Controller

- AXI local bus interface

Documentation

Please contact us to receive the latest version of the datasheet.

Utilization Numbers

Please contact us for utilization number.