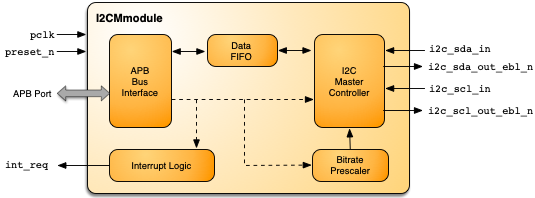

I2CMmodule

Inter-Integrated Circuit (I2C) Master Module

The Inter-IC bus, or I2C bus is a two wire serial bus. It supports multi-master applications with its built-in arbitration scheme. The I2C bus is widely used as a peripheral extension bus and to interface with configuration memories.

The I2CMmodule provides a versatile master controller that can be integrated in FPGA's and ASIC's. The design is technology neutral which simplifies its use and reuse.

The module is designed to limit the processor overhead by reducing the number of interrupt requests. The built-in data buffer size can be configured according to the application requirements.

Block Diagram

Features

- I2C standard compliant

- Supports 100kbps and 400kbps mode

- Supports 7-bit device address format

- Multi-master collision detection and bus arbitration

- Data buffer memory

- Automatic receive/transmit data sequencing

- Support of 1/2/3 byte internal address format

- Programmable message length

- Programmable baudrate generator

- Industry standard AMBA APB host interface

- Full synchronous design

- Technology independent, vendor independent

Implementation Features

- Register or memory based message buffer.

- The message buffer size is selectable, enabling the optimal usage of the available gates.

- Fully synchronous design: one global clock, one global asynchronous reset.

- Technology independent implementation. This design can be used for any technology as long as timing constraints are met.

Deliverables

- VHDL source code

- Simulation testbench

- Timing constraints file

- Synthesis script

- User Guide

Datasheet

Please contact us