SPIMmodule

Serial Peripheral Interface (SPI) Master Module

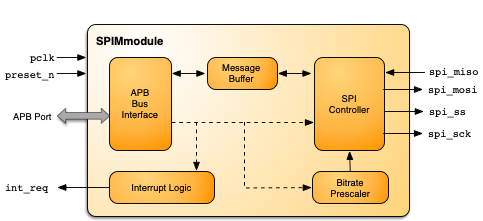

The SPIMmodule is part of Inicore's IPmodule family. The serial peripheral interface (SPI) protocol is often used to connect peripheral devices to a CPU. Several slave devices can be connected to the same bus. Since it is a serial bus, the pin count is low.

The SPIMmodule is a single master controller and uses a message queue based architecture. A message consists of the command, transmit data and receive data field. The command field defines the length of the SPI access (1-32 bits, or continued in the next command), the selected slave device, the SS to SCK delay and the delay after transfer control. Using the queue, several SPI commands can be executed without processor interaction.

A range of messages can be selected to be sent by the SPI controller. There is a wrap mode to enable continuously sending the same messages.

The SPI controller supports all standard modes. The clock phase and clock polarity can be configured as well as the bit rate and slave select polarity.

Block Diagram

Features

- Standard SPI single master

- Full duplex operation

- Programmable frame length, transfer delay, ss-to-sck delay, slave select polarity

- Continous re-transfer mode

- Supports all SPI modes: configurable clock polarity and phase

- Message queue buffer

- Programmable bitrate

- Local interrupt controller

- Industry standard AMBA APB host interface

- Full synchronous design

- Technology independent, vendor independent

Deliverables

- VHDL source code

- Simulation testbench

- Timing constraints file

- Synthesis script

- User Guide

Datasheet

Please contact us